> REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

# Dual Band VCO based on High Quality factor Switched Interdigital Resonator for Ku band using 180 nm CMOS Technology

## Islam Mansour, Mohamed Aboualalaa, Ahmed Allam, Adel B. Abdel-Rahman, Mohammed Abo-Zahhad, and Ramesh K. Pokharel

Abstract- A dual band and low phase noise Ku-band voltage-controlled oscillator (VCO) using 180 nm CMOS technology is presented in this brief. The proposed VCO employs a switched notch filter that can operate in the low and high band depends on the state of nmos transistor and has a quality factor that is higher than that of a conventional inductor-capacitor (LC) resonator. The proposed resonator doubles the quality factor compared to LC in the technology and reduces the total die area. The first band is realized by the switched interdigital resonator when nmos transistor is in the off state. Furthermore, the second band is realized by turning nmos transistor to the on state which is located between two fingers in the proposed resonator. The chip is implemented in 180nm CMOS technology, and found that the proposed VCO operates from 15.5 ~ 16.7Hz (low band) and 16.6 ~ 17.4 GHz (high band). At 1.8 V power supply, the power consumption of the oscillator core is 5.4mW and 7.2mW in the low and high-frequency bands respectively. The measured phase noise is -107 dBc/Hz at 1MHz offset from 16.7 GHz carrier frequency.

*Index Terms*— CMOS; dual-band; Ku-band; notch filter; switched interdigital resonator; Voltage Controlled Oscillator.

### I. INTRODUCTION

THE voltage-controlled oscillator (VCO) is one of the most important circuit blocks of the transmitter and the receiver front-end. The phase noise and frequency tuning range are the most essential design criteria; low power consumption, ease of system integration, and output power are other important considerations for VCOs design. To achieve these design criteria, the challenge is in designing high-quality factor LC

Manuscript received January 22, 2018; accepted March 14, 2018. This work was supported in part by Egypt–Japan University of Science and Technology, in part by the Grant-in-Aid for Scientific Research under Grant JP16K06301, in part by the VLSI Design and Education Center, University of Tokyo in Collaboration with Cadence and Keysight Corporations, and in part by the Center for Japan–Egypt Cooperation in Science and Technology (E-JUST Center), Kyushu University. This brief was recommended by Associate Editor N. M. Neihart. (*Corresponding author: Islam Mansour.*)

I. Mansour, M. Aboualalaa, and A. Allam are with Egypt–Japan University of Science and Technology, Alexandria 21934, Egypt (e-mail: islam.elgelb@ ejust.edu.eg).

A. B. Abdel-Rahman is with Egypt–Japan University of Science and Technology, Alexandria 21934, Egypt, and with the Electrical Engineering Department, Faculty of Engineering, South Valley University, Qena 83523, Egypt.

M. Abo-Zahhad with Egypt–Japan University of Science and Technology, Alexandria 21934, Egypt, and with the Electrical and Electronics Engineering Department, Faculty of Engineering, Assiut University, Asyut 71515, Egypt.

R. K. Pokharel is with the Faculty of Information Science and Electrical Engineering, Kyushu University, Fukuoka 819-0395, Japan (e-mail: pokharel@ed.kyushu-u.ac.jp).

tank circuit. The design of multiband or wideband RF front-ends on higher frequency bands is required for multifunction services. There are several design methods for dual-band VCO which provides an agile reconfiguration between dual bands. These methods include multi-core oscillators [1], variable inductors using switches to eliminate part of inductor [2-3], and switched capacitors [4-5]. However, these techniques suffer from the needed large area for the resonator. The design of dual-band VCOs introduces a considerable challenge because of the simultaneous requirements for wide frequency range, low phase noise and low power consumption. In the techniques of using switched LC tank circuit (inductors or capacitors), series MOSFET transistors (NMOS or PMOS) are used, the turn-on resistance of switches can cause the degradation of the quality factor of LC tank circuit and, consequently, the oscillator's phase noise. There are other techniques that used to achieve dual band VCO, for example, [6] use frequency doubler, together with the inductor of the low-band LC VCO and this method adds additional part (frequency doubler). Another method is to use two identical LC tanks coupled by capacitor and transformer to double the frequency tuning range [7] and this requires two inductors and two capacitors which lead to large area compared to the proposed single resonator VCO. Improving the phase noise is crucial in the oscillator's design and can be achieved using different ways for instance, using feedback capacitors to increase g<sub>m</sub>, improving the quality factor LC circuit and tail band pass filter at the second harmonic of the oscillation frequency [8-9].

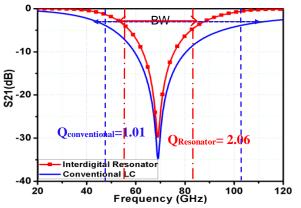

To design a single band VCO, LC tank resonator is usually employed, and loading of capacitor or varactor, which is essential to realize turning range, leads to decrease the loaded quality (Q-)factor of the LC-tank resonator. In this work, first instead of using LC tank resonator for a single band VCO, we employed a notch filter which has sharp skirt characteristic and lower bandwidth, which makes the Q-factor of the proposed resonator higher (almost double) than that of an LC tank resonator. Also, the proposed notch filter is switched that makes VCO operates in two band.

#### **II. CIRCUIT DESIGN**

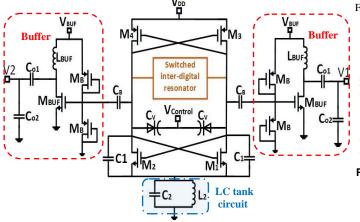

Fig. 1 illustrates the schematic of the proposed dual-band VCO. It consists of a cross-coupled NMOS pair (M1-M2), a cross-coupled PMOS (M3-M4)  $g_m$  cell to improve the phase noise, a switched interdigital resonator with NMOS transistor to act as a switch and the interdigital resonator works as narrow band stop filter and it resonant frequency is controlled by the

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TCSII.2018.2817499, IEEE Transactions on Circuits and Systems II: Express Briefs

#### > REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

NMOS transistor, junction varactor capacitor  $C_v$  for frequency tuning extension, a feedback capacitor (C<sub>1</sub>) to increase the negative transconductance, and a LC tank circuit (C<sub>2</sub>, L<sub>2</sub>) that works as current source and operates at  $2\omega_{osc}$  to eliminate the second harmonic and enhances the phase noise, where  $\omega_{osc}$  is the operating frequency. The switch in the interdigital resonator is used to select which band the VCO will operate whereas the control voltage V<sub>Control</sub> is used to fine tune the oscillation frequency at the high/low-frequency band. An inductor loaded common source configuration (M<sub>BUF</sub>, L<sub>BUF</sub>) used as an output buffer driving a 50 ohms impedance.

Due to the U-shape of the resonator and interdigital capacitors realized between the arms of U-shape, the overall size of the proposed resonator is reduced compared to the LC-tank resonator so that overall chip size is smaller than other reported VCOs in the same technology. Therefore, the proposed VCO has an area efficiency and achieves wide frequency tuning range compared to other published designs as it can operate in two bands using the same  $g_m$  cell and LC tank circuit by adjusting the  $V_{sw}$  value. the phase noise enhances by improving the performance of LC tank circuit (notch filter) as the implemented notch filter doubles the quality factor.

Fig. 1. Schematic of the dual-band VCO based on the switched resonator.

#### A. Switched Interdigital Resonator

A spiral inductor usually encounters a self-resonance at K-band or higher, therefore VCO design at K-band or beyond is very challenging. The proposed method employs a resonator where the resonance frequency is based on the length of the resonator, therefore the proposed method alleviates the above problem of self-resonance, and gives an alternative design approach of VCO at K-band and beyond. The proposed switched interdigital resonator consists of U-shape inductor, interdigital capacitor and NMOS transistor that acts as (off/on) switch by adjusting the gate voltage. Both the U shape inductor and interdigital capacitor are implemented in top metal layer M6 because it has the smallest sheet resistance.

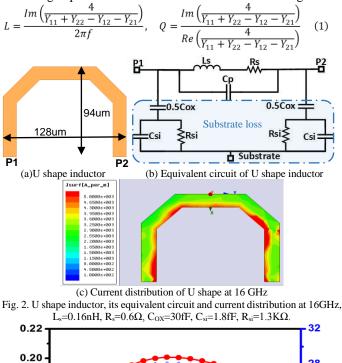

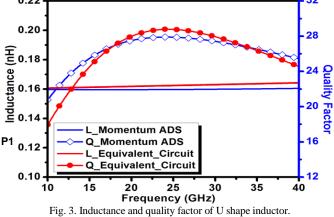

Starting by the U shape inductor and its performance is made using a 2.5D simulator (momentum ADS). From the S-parameters the equivalent circuit of the proposed inductor and this circuit consists of an inductor ( $L_s$ ) in series with resistor ( $R_s$ ) that represents loss, this combination in parallel with coupling capacitor ( $C_p$ ) and the substrate loss in the form of  $C_{ox}$ ,  $R_{si}$ , and  $C_{si}$  [9]. Fig.2 illustrates the U shape inductor, its equivalent circuit and the current distribution at 16 GHz, the area of U shape inductor is 0.012 mm<sup>2</sup>. The differential inductance and quality factor of the U shape inductor are calculated using the following expressions and those values are shown in Fig.3.

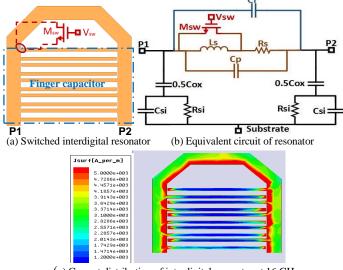

The switched interdigital resonator consists of U-shape inductor, finger capacitor that has better quality factor compared to the MIM capacitor and NMOS transistor as shown in Fig.4. Also, the equivalent circuit and the current distribution of the interdigital resonator at 16 GHz where the current is focused on the corners are shown in Fig.4. The equivalent circuit of interdigital resonator is the same as the U shape inductor in addition to the finger capacitor ( $C_f$ ) and the nmos transistor ( $M_{sw}$ ) that acts as a switch and controlled by its gate voltage  $V_{sw}$ .

The benefits of proposed switched interdigital resonator are not only it has a small size which is 0.015 mm<sup>2</sup> compared to the size of conventional LC (L=0.16nH and C=38fF) circuit which is 0.056 mm<sup>2</sup> but also it acts as notch filter with high quality factor ( $Q_{Resonator}$ ) that reaches 2.06 while the conventional one has a quality ( $Q_{Conventional}$ ) of 1.01 so the proposed resonator improves the quality factor by 100% compared to the LC from the technology (where the quality factor is the ratio between the center frequency and the 3dB bandwidth) and the high Q of interdigital resonator is due to a low resistance in series with the inductor. The proposed resonator can work in two different This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TCSII.2018.2817499, IEEE Transactions on Circuits and Systems II: Express Briefs

#### > REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

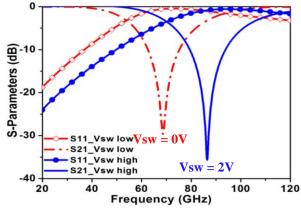

frequencies depending on the value of  $V_{sw}$ , when  $V_{sw}$  equals 0 or 2V, it works at low or high frequency band, respectively and its response is illustrated in Fig.5. The resonance frequency of proposed notch filter is 68GHz and 88GHz in the low and high frequency band, respectively while the VCO oscillates at Ku-band and this because of the oscillation frequency is determined by interdigital resonator, varactor capacitance, drain parasitic capacitance and buffer input capacitance.

(c) Current distribution of interdigital resonator at 16 GHz Fig. 4. Interdigital resonator, its equivalent circuit and its current distribution at 16 GHz,  $C_f=38fF$ ,  $M_{sw}(W/L)=96\mu m/0.18\mu m$ ,  $V_{sw}=0V$  or 2V.

(a)The response of proposed resonator and LC circuit from the technology.

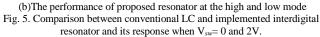

The equivalent circuit model of the oscillator is cleared in Fig. 6(a), the symmetric resonator is represented by  $L_{res}$ ,  $C_{res}$  and  $R_s$  is used to represent the loss in interdigital resonator. Varactors for frequency tuning are modeled with capacitor  $C_v$  in series with a resistor  $R_v$ . The total parasitic capacitance of the MOS transistors (NMOS and PMOS) are represented by  $C_{NMOS}$  and  $C_{PMOS}$ , and  $g_m$  and  $g_0$  are small transconductance and output conductance of the transistors, respectively. From Fig.6, the tank inductance  $L_{tank}$ , tank capacitance  $C_{tank}$ , the tank loss  $g_{tank}$  and effective negative conductance  $-g_{active}$  are given by:

$$L_{tank} = L_{res}, \qquad C_{tank} = C_{res} + 0.5(C_V + C_1 + C_{PMOS} + C_{NMOS})$$

(2)

$$2g_{tank} = g_{on} + g_{op} + g_v + g_{res} , \ 2g_{active} = g_{mn} + g_{mp}$$

(3)

Where  $g_{res}$  and  $g_v$  are the effective parallel conductance of the resonator and varactors, respectively.

The oscillation frequency is determined by the value of the inductance and capacitance of tank circuit as described in the following equation.

$$\omega_{osc} = \frac{1}{\sqrt{L_{tank} * C_{tank}}} \tag{4}$$

Taking the effect of parasitic inductance and capacitance in the oscillation frequency is crucial especially in the high frequency. In the proposed VCO, the interdigital resonator, the inductors, and all the all transmission lines have been designed and characterized separately using ADS Momentum electromagnetic simulator then added as S-parameters block in the ADS simulator to take their parasitic components into consideration and not effect on the oscillation frequency. Fig.6 (b) shows the percentage of phase noise contributed from different sources when the oscillation frequency is 16 GHz.

(a)Equivalent model of proposed VCO. (b) Phase noise contribution Fig. 6. Equivalent oscillator model and contribution of the phase noise at 16 GHz.

# III. IMPLEMENTATION AND EXPERIMENTAL RESULTS

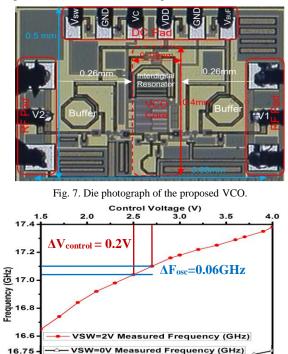

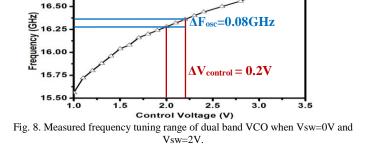

The proposed VCO is fabricated in 180nm CMOS technology. The chip micrograph is shown in Fig.7. The total chip area is  $0.68 \times 0.5 \text{ mm}^2$  including the two output buffers, DC pads and output pads, while the active area of VCO core only is  $0.16 \times 0.4 \text{ mm}^2$ . The DC power consumption of the proposed VCO excluding output buffers is 5.4mW and 7.2mW from a supply voltage of 1.8 V in the low and high frequency band, respectively based on the status of V<sub>sw</sub> is low or high voltage, while the two output buffers consume 5mA from a 1.8V supply. The measured frequency tuning ranges are shown in Fig. 8, the measured oscillation frequency varies from 15.5–16.7GHz (7.5%) and 16.6–17.4GHz (4.7%) when V<sub>sw</sub>=0 and 2V,

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TCSII.2018.2817499, IEEE Transactions on Circuits and Systems II: Express Briefs

#### > REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

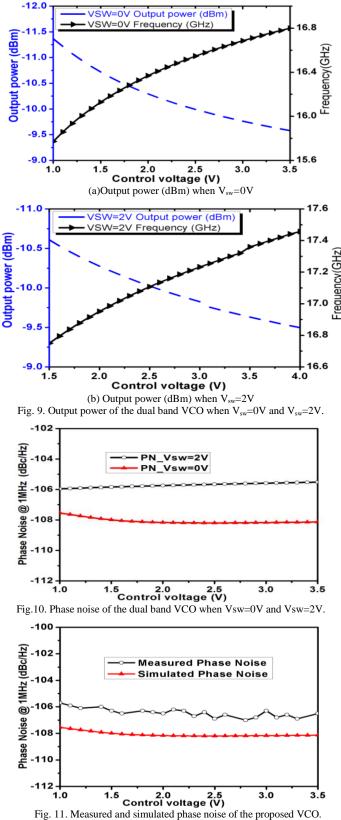

respectively. As clear the rate the oscillation frequency changes with the control voltage is 0.4GHz/V and 0.3GHz/V in the low and high frequency band, respectively. The output power driving a 50 $\Omega$  load is shown in Fig.9 when V<sub>sw</sub> is 0 and 2V.

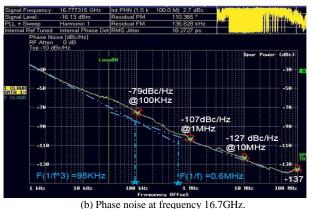

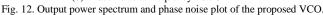

The phase noise of the VCO at 1MHz offset is illustrated in Fig. 10, when  $V_{sw} = 0$  and 2V, the phase noise is approximately -108 and -106 dBc/Hz, respectively. The phase noise degrades by 2 dB between two bands and this because of the quality factor of the notch filter in the high band which is  $1.7 (V_{sw}=2V)$  is lower than the one which is 2 in the low band ( $V_{sw}=0V$ ). This reduction in the phase noise and the power dissipated of the VCO core is 5.4mW and 7.2mW in the low and high frequency band, respectively lead to about 3 dB degradation in FoM between the low and high band. The measured and simulated phase noise at 1MHz offset is plotted in Fig.11. There is about 1.5 dB difference between the measured and simulated phase noise and this due to the losses of cables which are maximum at Ku frequency band and another reason is the noisy DC power used in the measurement while the simulation uses an ideal and pure DC power supply. The measured PN at 1MHz offset changes from -105.9 dBc/Hz to -107 dBc/Hz and from -104.8 dBc/Hz to -105.6 dBc/Hz in the low and high frequency band, respectively. The measured FoM,  $FoM^{T}$  and  $FoM_{A}$  when the oscillation frequency is 16.7 GHz are 185dBc/Hz, 182dBc/Hz and 189.7dBc/Hz, respectively, while the simulated one is 186.5dBc/Hz, 183.5dBc/Hz and 191dBc/Hz at the same oscillation frequency.

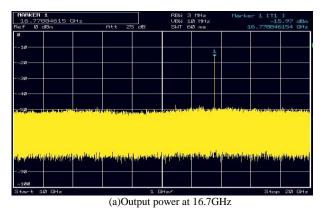

Fig.12 illustrates the measured RF output spectrum plot and the phase noise plot of the proposed VCO when the oscillation frequency equal to 16.7GHz. The measured output power when

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TCSII.2018.2817499, IEEE Transactions on Circuits and Systems II: Express Briefs

#### > REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

the oscillation frequency 16.77 GHz is -10 dBm after calibration as there is about 6 dB loss. From the phase noise spectrum, the measured phase noise is -79, -107 and -127dBc/Hz at 100KHz, 1MHz and 10MHz offset. The 1/f corner frequency and  $1/f^3$  corner frequency are 0.6MHz and 95KHz, respectively.

The proposed switched interdigital resonator VCO shows better or comparable performances in the ever – reported VCOs implemented using 180nm CMOS technology concerning frequency tuning range, phase noise, power consumption, area, FoM, FoM<sup>T</sup> and FoM<sub>A</sub>, as illustrated in Table I.

#### IV. CONCLUSION

A switched interdigital resonator VCO using 180nm CMOS technology is presented in this paper. The proposed notch filter diminishes the chip area, achieves wide frequency tuning range and enhances the phase noise. The VCO has a small area of 0.34 mm<sup>2</sup> and exhibits dual band tuning range low band 15.5–16.7GHz (7.5%) and high band 16.6–17.4GHz (4.7%). The measured phase noise at 1MHz offset frequency from the carrier 16.7GHz is -107 dBc/Hz. The proposed VCO achieves FoM<sub>A</sub> of 189.7 dBc/Hz and 186.7 dBc/Hz in the low and high frequency, respectively.

| TABLE I.                                                            |            |            |                 |            |              |      |            |                  |                |

|---------------------------------------------------------------------|------------|------------|-----------------|------------|--------------|------|------------|------------------|----------------|

| Performance comparison of VCOs implemented in 180nm CMOS technology |            |            |                 |            |              |      |            |                  |                |

| Ref                                                                 | Fre.       | TR         | $V_{\text{DD}}$ | $P_{DC}$   | PN           | Area | FoM        | FoM <sup>T</sup> | FoMA           |

| [1]                                                                 | 7.4<br>24  | 7.1<br>7.8 | 1.5<br>1.5      | 7.5<br>9.7 | -112<br>-100 | 0.67 | 180<br>178 | 177<br>175       | 181.7<br>179.3 |

| [11]                                                                | 24.2       | 2.2        | 0.65            | 7.8        | -100         | 0.42 | 179        | 165.6            | 182.7          |

| [12]                                                                | 25         | 2.4        | 1.5             | 13.2       | -104         | 0.4  | 180        | 167.6            | 183.9          |

| [13]                                                                | 15<br>30   | 1.6<br>1.6 | 2<br>2          | 52<br>52   | -112<br>-104 | 1.1  | 179<br>177 | 162<br>160       | 178.1<br>176.3 |

| This                                                                | 16.1<br>17 | 7.5<br>4.7 | 1.8<br>1.8      | 5.4<br>7.2 | -107<br>-105 | 0.34 | 185<br>182 | 182<br>175       | 189.7<br>186.7 |

$\begin{array}{l} FoM = PN + 20 \, \log \left( \omega_0 / \, \Delta \omega \right) - 10 \, \overline{\log(P_{DC}(1 \, mW))}, \, FoM^T = FoM + 20 \log(TR/10) \\ and \, FoM_A = FoM - 10 \log(Area(mm^2)). \end{array}$

Fre: GHz, PN @1MHz,  $V_{DD}$ : V,  $P_{DC}$ : mW, PN, FoM, FoM<sup>T</sup> and FoM<sub>A</sub> in dBc/Hz Area is the total area which the area of VCO core and the output buffers in  $mm^2$

#### REFERENCES

- Sen Wang and Chang-Yuan Xiao, "A 7/24-GHz CMOS VCO with High Band Ratio Using a Current-Source Switching Topology," *IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control*, vol. 63, no. 5, pp. 790 - 795, May 2016.

- [2] J. Zhang, N. Sharma and K. O. Kenneth, "21.5-to-33.4 GHz Voltage-Controlled Oscillator Using NMOS Switched Inductors in CMOS," *IEEE Microwave and Wireless Components Letters*, vol. 24, no. 7, pp. 478-480, July 2014.

- [3] A. Agrawal, and A. Natarajan, "Series Resonator Mode-Switching for Area-Efficient Octave Tuning-Range CMOS LC Oscillators," *IEEE Transactions on Microwave Theory and Techniques*, vol. 65, no. 5, pp. 1569-1579, May 2017.

- [4] Sheng-Lyang Jang, and Sanjeev Jain, "Dual C- and S-Band CMOS VCO Using the Shunt Varactor Switch," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 23, no. 9, pp. 1808 - 1813, September 2015.

- [5] Islam Mansour, H.Mosalam, Ahmed Allam, Adel B. Abdel-Rahman and Ramesh K. Pokharel, "K Band Low Power Voltage Controlled Oscillator Using 180 nm CMOS Technology With A New High-Quality Inductor," in Proc. of IEEE International Conference on Ubiquitous Wireless Broadband (ICUWB), October 2016.

- Z.-Y. Yang and R. Y. Chen, "High-performance low-cost dual 15 GHz/30 GHz CMOS LC voltage-controlled oscillator," *IEEE Microwave Wireless Components Letters*, vol. 26, no. 9, pp. 714–716, September 2016.

- [7] G. Li, L. Liu, Y. Tang, E. Afshari, "A low-phase-noise wide-tuning-range oscillator based on resonant mode switching", *IEEE J. Solid-State Circuits*, vol. 47, no. 6, pp. 1295-1308, June 2012.

- [8] Marco Garampazzi, Paulo Mendes, Nicola Codega, Danilo Manstretta and Rinaldo Castello, "Analysis and Design of a 195.6dBc/Hz Peak FoM P-N Class-B Oscillator with Transformer-Based Tail Filtering," *IEEE Journal* of Solid-State Circuits, vol. 50, no. 7, pp. 790 - 795, July 2015.

- [9] S.-L. Liu, K.-H. Chen, and A. Chin, "A dual-resonant mode 10/22-GHz VCO with a novel inductive switching approach," *IEEE Transactions on Microwave Theory and Techniques*, vol. 60, no. 7, pp. 2165–2177, July 2012.

- [10] Fengyi Huang, Jingxue Lu, Nan Jiang, Xiaowen Zhang, Wengang Wu, and Yangyuan Wang, "Frequency-Independent Asymmetric Double-π Equivalent Circuit for On-Chip Spiral Inductors: Physics-Based Modeling and Parameter Extraction," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 10, pp. 2272- 2283, October 2006.

- [11] J. Yang, C.-Y. Kim, D.-W. Kim, and S. Hong, "Design of a 24-GHz CMOS VCO with an asymmetric-width transformer," *IEEE Transactions* on Circuits System II, vol. 57, no. 3, pp. 173–177, March 2010.

- [12] T.-Y. Lian, K.-H. Chien, and H.-K. Chiou, "An improved Gm boosted technique for a K-band Cascode Colpitts CMOS VCO," *IEEE Asia-Pacific Microwave Conference Proceedings (APMC)*, pp. 685- 687, November 2013.

- [13] H. H. Hsieh, Y. C. Hsu, and L. H. Lu, "A 15/30-GHz dual-band multiphase voltage-controlled oscillator in 0.18-µm CMOS," *IEEE Transactions on. Microwave and Theory Techniques*, vol. 55, no. 3, pp. 474–483, March 2007.